Das NVMe-Protokoll bearbeitet mehrere Befehle gleichzeitig und erreicht damit eine deutlich schnellere Performance, als das in herkömmlichen SATA-SSDs verwendete AHCI. Zudem kommt NVMe mit einem geringeren Verwaltungsaufwand und vereinfachter Befehlsverarbeitung. Lesen Sie hier eine technische Einführung unseres Autors Hermann Strass.

Von Hermann Strass

Mit NVMe (Non-Volatile Memory Express) kann der Anwender das volle Leistungs- und Latenzpotenzial von Flash-Speicher, wie höhere Ein-Ausgabe-Leistung durch die optimale Unterstützung von mehr Prozessorkernen, mehr Kanälen je Gerät, Ein-Ausgabe-Funktionspfaden und -Warteschlangen, nutzen. NVMe benötigt keinen Verwaltungsaufwand wie die Befehlsverarbeitung bei SCSI und ATA I/O. NVMe realisiert eine vereinfachte Befehlsverarbeitung, weil alle Befehle gleich groß und in der gleichen Position verfügbar sind. NVMe ist weniger komplex, effizienter, bedienerfreundlicher und leichter zu handhaben als herkömmliche Systeme.

Das NVMe-Protokoll

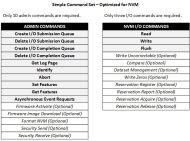

NVMe ist ein skalierbares Protokoll das für den effizienten Transport über PCIe zur Speicherung auf NAND-Flash optimiert wurde. Es wird derzeit vorwiegend in PCIe-Halbleiterlaufwerken eingesetzt. Das Protokoll nutzt einen einfachen, rationalisierten Befehlssatz aus 13 Befehlen, wie in Tabelle 1 gezeigt. Zur Optimierung von Speicherung und Auslesen werden bis zu 64.000 Befehle (64K) je Warteschlange (queue) in bis zu 64.000 Ein/Ausgabe-Warteschlangen zur parallelen Verarbeitung eingerichtet. Dazu ist im Hauptrechner ein gepaarter Auftrags- und Erledigungs-Warteschlangenmechanismus eingerichtet. Die übergeordnete Software stellt Befehle in die Auftrags-Warteschlange. Die NVMe-Steuerung (controller) im Gerät stellt Erledigungsbefehle in die zugehörige Erledigungswarteschlange. Mehrere Auftragswarteschlangen können die Erledigung in einer einzigen Erledigungswarteschlange melden, vorausgesetzt die Steuerung unterstützt die Entscheidung nach unterschiedlichen Prioritäten. Die Unterbrechungssteuerung gemäß Message-Signaled Interrupts Extended (MSI-X) wird ebenfalls unterstützt. Wahlweise wird die Unterstützung für viele Funktionen aus dem Großrechnerbetrieb angeboten, wie Ende-zu-Ende Datenschutz (kompatibel mit T10-DIF- und DIX-Standards), erweiterte Fehlerberichterstattung, autonome Anpassung der Stromversorgung in den angeschlossenen Geräten und Gruppierung der Eigenschaften (hinting).

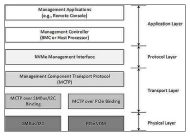

Das NVMe-MI transportiert die Befehle für die Systemverwaltung. Folgende Elemente bilden die Systemverwaltung:

- Inventory

- Configuration

- Health-Status-Monitoring

- Change-Management

Mit der Ein-/Ausgabe-Virtualisierung einer Quelle Single Root I/O Virtualization (SR-IOV) kann ein PCIe-Gerät so virtualisiert werden, dass es als mehrere Geräte verfügbar ist. So werden Ein-/Ausgabe-Flaschenhälse in Server-Umgebungen vermieden und die Datenraten bis zur vollen PCIe-Bandbreite angehoben.

Es gibt eine Programmschnittstelle für die nebenläufige Verwaltung der im Feld tauschbaren Einheiten (FRU). Eine Field Replaceable Unit (FRU) ist eine Baugruppe (Platine), ein Teil oder eine Untereinheit das schnell und leicht aus einem Computer oder einem anderen Gerät aus- und eingebaut werden kann. Der Anwender oder Techniker kann eine FRU direkt vor Ort tauschen. Er muss nicht das ganze Produkt oder System zur Reparatur ins Depot schicken.

Das NVMe-Protokoll bietet eine Auswahl von Funktionen:

- up to 64K I/O queues, with up to 64K commands per queue

- priority associated with each I/O queue with well-defined arbitration mechanism

- all information for a 4KB read request is in the 64B command itself

- efficient small random I/O operation

- efficient and streamlined command set

- MSI/MSI-X and interrupt aggregation

- no un-cacheable / MMIO register reads required

- a maximum of one MMIO register write is necessary

- multiple namespaces

- efficient I/O virtualization architectures like SR-IOV

- Multi-path I/O, including reservations

- robust error reporting and management capabilities

- End-to-end data protection (DIF/DIX)

Verschieden PCIe-Baugrößen

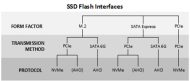

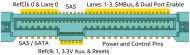

U.2: Die Baugruppen- und Steckverbindervariante U.2 (früher SFF-8639 oder multifunktionaler 6-fach ungeschirmter Steckverbinder) bietet sechs Kanäle für Hochgeschwindigkeitsübertragung mit folgenden Wahlmöglichkeiten:

- Single port SATA (1 lane)

- Dual port SATAe (2 lanes)

- Dual port SAS (2 lanes)

- MultiLink SAS (4 lanes)

- Four port PCIe (4 lanes)

Häufig genutzt werden vier PCIe-Kanäle oder ein Mix aus PCIe mit zwei SAS-Kanälen und einem SATA-Kanal in einem NVMe-Gestell um Baugruppenträger mit mehreren Flash-Platinen in einem 2,5-Zoll Format (SFF-8223, EIA-720). Derzeit sind 2,5-Zoll-Gestelle die meistverkauften Baugruppenträger weil sie einfach einsetzbar sind, Austausch im laufenden Betrieb bieten sowie einfach einsetzbar und klein sind.

M.2: Die M.2- Baugruppen (Steckkarten auf Basisplatinen oder auf Motherboards) gibt es in vielen Baugrößen: in Breiten von 12 mm, 16,5 mm, 22 mm und 30 mm sowie in Längen von 16 mm, 26 mm, 30 mm, 80 m und 110 mm. Einseitig (single-sided: S1 bis S3) und zweiseitig (double-sided: D1 bis D3) bestückte Versionen mit unterschiedlichen Bauhöhen für Komponenten sind definiert. Andere Schnittstellen, wie USB und I²C sind ebenfalls spezifiziert. Nicht alle verfügbaren Kombinationen werden genutzt. Die Baugruppenträger können auch mechanisch codiert werden für SATA (Sockel 2) oder PCIe x4 (Sockel 3). Die Längen 42 mm, 80 mm und 110 mm sind am populärsten. M.2 bietet die kleinste Baugröße mit PCIe für den Computerstart oder für maximale Speicherdichte.

SATAe: Mit dem SATA-Express-Steckverbinder (SATAe) werden Laufwerke in 2,5-Zoll Baugröße, Festplatten oder hybride Laufwerke angeschlossen. Es werden SATA- und PCIe-3.0-Kanäle in Kombination zur Verfügung gestellt. SATAe ist eine Kabelversion von SATA-3.0-Kanälen (6 Gbit/s) am Hauptrechneranschluss. Die PCIe-Kanäle bieten reines PCIe ohne zusätzliche Ebenen von Bus-Abstraktion.

BGA: Einige Anbieter haben eine BGA-Lösung für Einheiten in kleinen Baugrößen vorgeschlagen, wie 2-in1-Laptops.

Eigenständige Vorteile von NVMe

NVMe unterstützt eine große Anzahl von umfangreichen Warteschlangen und Befehlen je Warteschlange. Das ermöglicht Parallelverarbeitung in mehreren Rechnerkernen im System mit Unterstützung von Non-Uniform Memory Architecture (NUMA). Nichtverriegelte Befehlsausgabe und -beendigung ermöglicht kürzere Latenz und umgeht alle SCSI-Ebenen. Die 64-Bit-Befehle werden über einfache PCIe-Register flexibel und ohne Beeinträchtigung ausgegeben.

Mit der Controller Memory Buffer-Funktion ist es bei NVMe möglich die Befehle schon im Speicher des Hauptrechners bereit zu stellen. Damit ist es nicht mehr nötig, dass die Gerätesteuerung die Befehlspuffer mit Hilfe von PCIe-Lesefunktionen auslesen muss. Die NVMe-Schnittstelle arbeitet weitgehend unterbrechungsfrei. Der Schwerpunkt liegt auf der Übertragung zusammenhängender Speicherblöcke anstatt auf der Übertragung von einzelnen SCSI-Befehlen. Damit sind die Latenzzeiten niedriger als bei anderen Protokollen. Der NVMe-Zuteilungsmechanismus verbessert die Flexibilität durch die Zuteilung von Prioritäten auf Befehlsebene. Damit werden die Werte für den Leistungsvertrag Service-Level-Agreement (SLA) verbessert. Im Protokoll sind Reservierungen für Anwendungen in Datenzentralen vorgesehen. Professionelle Betriebssysteme bieten integrierte Softwaretreiber für NVMe zur vereinfachten Nutzung.

NVMe stellt im Hauptrechner auch einen zusätzlichen Pufferspeicher für unkritische Datenstrukturen bereit. So können Gerätesteuerungen ohne DRAM den Systemspeicher nutzen. Das ist vorteilhaft für Geräte- und mobile NVMe-Steuerungen.

Wie NVMe das Anwendererlebnis verbessert

NVMe bietet viele Vorteile gegenüber Flash-Speicher an SATA oder SCSI. Der direkte Anschluss an den Hauptrechner (CPU) ermöglicht kürzere Latenzzeiten im Vergleich mit der Anbindung über Ein-/Ausgabesteuerungen, Multiplexer oder Speichernetzwerke. Die skalierbare Leistung bis zu einem GByte/s pro Kanal wird durch die Nutzung von Industriestandards, wie NVMe und PCIe 3.0, erreicht. Derzeit werden 40 PCIe-Kanäle von einer CPU unterstützt. In Zukunft können auch 48 Kanäle unterstützt werden.

Das NVMe-Protokoll unterstützt unterschiedliche autonome Energiewechsel, wie Low Power Link (L 1.2). Das NVMe-Protokoll gibt es für Geräte in verschiedenen Gerätebaugrößen, also beispielsweise M.2, SATAe, SFF-8639 (U.2) und SFF-8680, wie oben angegeben.

Vorteilhafte Funktionen von NVMe

Hinting, Attribute Pools, Streams: Die Befehle des Dataset Management (DSM) in NVMe bieten ein umfangreiches Gerüst für die Gruppierung der Eigenschaften. DSM erlaubt Gruppierung der Eigenschaften per Ein-/Ausgabe (in-band) ebenso wie Out-of-band-Gruppierung (Nebenläufigkeit) der Eigenschaften. Die Gruppierung der Eigenschaften (hinting) umfasst: Ein-/Ausgabe-Klassifikation, Richtlinienzuweisung und -einhaltung. Objekte und Ein-/Ausgabedaten werden nach Klassen identifiziert oder gruppiert. Speicherrichtlinien werden den Ein-/Ausgabe- und Objektklassen zugeordnet, deren Einhaltung im Speichersystem erzwungen wird. Die zukünftigen NVMe-Spezifikationen werden Quality of Service (QoS) in Form Mediengruppierungen (bands) festlegen, die in NVMe Gruppierung von Merkmalen (attribute pools) heißen. In diesen Attribute Pools wird die Servicequalität (QoS) durch die Angleichung der Speicherart (SSD, SAS/SATA HDD oder NVDRAM) an die Anforderungen der Anwendung erreicht. Das wird weiter unten genauer beschrieben. Datenströme (streams) bezeichnen Gruppen von Daten die derselben physikalischen Adresse zugeordnet sind und deshalb gemeinsam zugeordnet und gelöscht werden können. Die zukünftige NVMe-Spezifikation für Datenströme definiert Datenstromsteuerungsbefehle und Datenstromkennungen für Ein-/Ausgabe-Schreibbefehle. Diese wiederum sind dann Eigenschaften in Gruppierungen (hints), die Datengruppen identifizieren.

Streams: In NVMe können die Anwendungen logische Blöcke als Teile von unterschiedlichen Datenströmen bestimmen. Diese Information nutzt das Gerät als Technik zur physikalischen Zuordnung um die Aufräum-Prozedur (garbage collection) zu minimieren. So kann der Schreibvermehrungsfaktor (write amplification factor) verringert werden, weil die Speichereinheit alle physikalischen Medien, die einem Datenstrom zugeordnet sind, freigeben kann oder weil andere leistungsbezogenen Verbesserungen möglich sind. Wenn eine Anwendung Nutzerdaten, die dieselbe erwartete Lebensdauer haben, zusammenfügen und speichern kann, dann wird unnötige Datenverarbeitung vermieden sowie die Gesamtlebensdauer und Leistung von NAND-Flash verbessert. So kann beispielsweise der Hauptrechner die logischen Blöcke eines Datenstroms gemeinsam löschen oder alle diese Blöcke gleichzeitig freigeben. Zusätzlich werden in der zukünftigen Spezifikation für Datenströme auch beschleunigte Hintergrundverfahren (accellerated background operations) definiert. Es kann sein, dass sich die Abläufe beim beschleunigten Hintergrundverfahren geringfügig mit den Lese- und Schreibanforderungen überlappen.

Attribute Pools: Mediengruppierungen mit einer gemeinsamen Gruppe von Merkmalen (Kapazität, Leistung, Haltbarkeit/Dauerhaftigkeit und Langlebigkeit) werden in der amerikanischen Spezifikation wahlweise als Attribute-Pools oder bands of media bezeichnet. In NVMe kann eine Speichereinheit mehreren Physikalischen Speicher(lagern) angehören und somit in unterschiedlichen Medien mit unterschiedlichem QoS für unterschiedliche Namensräume oder logische Adressbereiche genutzt zu werden. Die Speichereinheit kann dazu wahlweise einen Zwischenspeicher oder eine hierarchische Anordnung als Methode nutzen um die gewünschte QoS zu ermöglichen. Die Verwaltung der QoS solcher Speicher aus mehreren Speicherlagern geschieht mit Hilfe der Management Attribute Pools-Funktion. Die ‘Attribute Pools’ werden per Namensraum definiert. Ein einzelner Attribute Pool kann mehrere physikalische Speicher(lager) umfassen. Jeder Namensraum kann mehrere Attribute-Pools umfassen.

Dual-Port-Laufwerke: Der gemeinsame Namensraum von Laufwerken mit zwei Anschlüssen (dual ported) kann in zwei Domänen (Bereichen) existieren, wobei jeder ‘Port’ zu einem anderen Bereich (Server) gehört. Ein Multikanaltreiber sorgt für gleichmäßige Verteilung der Last durch eine zyklische Reihenfolge, wodurch ein höherer Datendurchsatz erreicht wird. Bei dieser Anordnung hat ein Hauptrechner zwei redundante Kanäle zur SSD. Nach einem Kanalfehler kann der Hauptrechner alle Ein-/Ausgabebefehle zu dem noch verfügbaren Kanal umleiten.

Der koordinierte Zugriff zu einem Laufwerk wird durch Reservations (Reservierungen) über dauerhafte Reservierungen/Freigaben, sogenannte Persistent reserve/release-Befehle (PR) gesteuert. Es gibt sechs Arten von Reservierungen, wie in Tabelle 2 gelistet. Zu einem bestimmten Zeitpunkt kann immer nur jeweils eine Reservierungsart gültig sein.

Falls beispielsweise ein Controller eine Write Exclusive-Reservierung unterstützt, kann nur der Hauptrechner der diese Reservierung hält, in dieses NVM schreiben. Allerdings können beide Hauptrechner aus diesem NVM lesen. Diese Variante arbeitet also wie eine Aktiv-passiv-Reservierung.

Typischerweise bevorzugen Cluster die Write Exclusive – Registrants only-Reservierungsvariante, bei der die Anmeldenden auch Schreibbefehle an die NVM-Geräte oder Namensräume senden können. So können zwei Hauptrechner gleichzeitig Befehle senden. Diese Variante arbeitet als Aktiv-aktiv-Reservierung. Dabei koordinieren sich die beiden Hauptrechner so, dass sie in unterschiedliche Adressbereiche schreiben, also beispielsweise in unterschiedliche logische Blockadressen (LBAs).

DIF/DIX-Unterstützung mit NVMe

Der Ende-zu-Ende-Datenschutz ist kompatibel mit der SCSI Protection Information, die als T10 DIF und SNIA DIX bekannt ist. NVMe unterstützt den gleichen Ende-zu-Ende-Datenschutz wie DIF. Die Art des Datenschutzes (Type1, Type2 oder Type3) wird festgelegt, wenn ein Namensraum formatiert wird. Sie wird in die Datenstruktur für den identifizierten Namensraum eingetragen.

Type1/Type3 wird in der Struktur des Namensraums unterstützt. Die DIX-Metadaten werden in einen eigenen Datenpuffer übertragen. Die NVMe-Steuerung prüft nur 2 Bytes aus der Prüfsumme (CRC) des Lese- oder Schreibbefehls. Bei Type1 prüft die Steuerung die letzten 4 Bytes der logischen Blockadresse (LBA) gegen den Expected Initial Logical Block Reference Tag (EILBRT) bei Lesebefehlen sowie gegen den Initial Logical Block Reference Tag (ILBRT) bei Schreibbefehlen. Entdeckt die NVMe-Steuerung eine Ungleichheit der Prüfsumme Cyclic Redundancy Check (CRC), wird dies dem Hauptrechner gemeldet, der dann das Korrekturverfahren einleitet.

Testverfahren für NVMe-Kompatibilität

Die Halbleiter-Testverfahren entsprechen JEDEC JC-64.8 oder SNIA SSS PTS und anderen Spezifikationen. Die Universität von New Hampshire (UNH) hat in ihrem Interoperability Lab (UNH-IL) zusammen mit der NVMe-Organisation ein robustes Interoperabilitätsprogramm entwickelt. Das UNH-IL hat umfassende Erfahrung mit Protokoll- und Kanal-Interoperabilität. Es hat diese Art von Dienstleistung bereits für viele andere Systeme mit unterschiedlichen Protokollen und Kanälen erbracht.

Zusammenfassung: NVMe einfacher und mit schnellerer Leistung

Mit NVMe kann der Anwender das volle Leistungs- und Latenzpotenzial von Flash-Speicher, wie höhere Ein-Ausgabe-Leistung durch die optimale Unterstützung von mehr Prozessorkernen, mehr Kanälen je Gerät, Ein-Ausgabe-Funktionspfaden und -Warteschlangen, nutzen. NVMe benötigt keinen Verwaltungsaufwand wie die Befehlsverarbeitung bei SCSI und ATA I/O. NVMe realisiert eine vereinfachte Befehlsverarbeitung, weil alle Befehle gleich groß und in der gleichen Position verfügbar sind. NVMe ist weniger komplex, effizienter, bedienerfreundlicher und leichter zu handhaben als herkömmliche Systeme.

- Flash-Serie 1: SAS oder SATA: Schnittstellen-Wissen für den richtigen Einsatz

- Flash-Serie 2: So lassen sich die Vorteile von Flash richtig nutzen

- Flash-Serie 3: So eignet sich Flash über PCIe

- Doc Storage: Was ist NVMe?

- Special All-Flash & SSDs« auf speicherguide.de